# Evaluation Guide

Featuring

ACCEL Schematic,

ACCEL P-CAD PCB,

and ACCEL PRO Route

ACCEL Technologies, Inc.

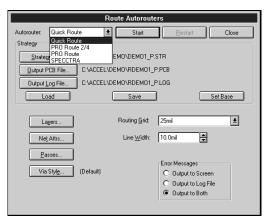

### Copyrights

Software Copyright ©1996 ACCEL Technologies, Inc. *Evaluation Guide* Copyright ©1996 ACCEL Technologies, Inc.

This software product is copyrighted and all rights are reserved. The distribution and sale of this product are intended for the use of the original purchaser only per the terms of the License Agreement.

This *Evaluation Guide* is copyrighted and all rights are reserved.

This document may not, in whole or part, be: copied; photocopied; reproduced; translated; reduced or transferred to any electronic medium or machine-readable form without prior consent in writing from ACCEL Technologies, Inc.

U.S. Government use, duplication, or disclosure is subject to RESTRICTED RIGHTS under applicable government regulations pertaining to trade secret, commercial computer software developed at private expense, including FAR 227-14 subparagraph (g)(3)(i), Alternative III and DFAR 252.227-7013 subparagraph (c)(1)(ii).

All trademarks and registered trademarks are properties of their respective owners.

ACCEL Technologies, Inc. 6825 Flanders Drive San Diego, CA 92121-2986 U.S.A.

Fax: 619/554-1019 BBS: 619/554-1018

Customer Service: 619/554-1000

Sales: 800/488-0680

ACCEL develops and markets design tools to meet the present and future needs of engineering professionals worldwide, who share our passion for innovation, excellence, and exceptional value.

# **Evaluation Guide Contents**

| ntroducing ACCEL EDA for Windows                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------|

| System overview; evaluation version limitations; using this guide.                                                          |

| Section 1, Installation and Setup                                                                                           |

| System requirements; installation instructions.                                                                             |

| Section 2, ACCEL EDA Basics                                                                                                 |

| User interface; loading files; viewing documents; zoom commands; units; styles; grids; libraries.                           |

| Section 3, Placing, Selecting, and Editing Objects19                                                                        |

| Placing objects; selecting objects; editing operations.                                                                     |

| Section 4, A Schematic Design Session3                                                                                      |

| Setting up your design; creating a simple schematic; working with your design; design verification; reports and output.     |

| Section 5, A PCB Design Session55                                                                                           |

| Setting up your design; initial board layout; routing connections; copper pouring; design verification; reports and output. |

| Section 6, Integrated Autorouting87                                                                                         |

| Setting up and running the integrated autorouters.                                                                          |

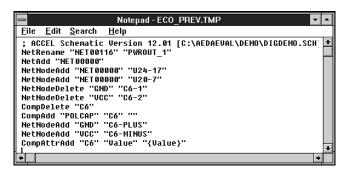

| Section 7, Linking the Pieces101                                                                                            |

| ECOs; cross-probing; shared libraries.                                                                                      |

| Taking the Next Step111                                                                                                     |

| Appendix A. Using P-CAD Files                                                                                               |

# Introducing ACCEL EDA

Thank you for taking the time to review this evaluation of ACCEL EDA, the premier schematic entry and printed circuit board design system for the professional designer. This guide is intended for designers having any level of Electronic Design Automation (EDA) tool experience; from the novice to the experienced user.

As a second generation Microsoft<sup>®</sup> Windows<sup>TM</sup> product line, ACCEL EDA is well-founded in a comprehensive specification based on years of research, field testing, and customer input. With roots in the popular P-CAD and Tango products, ACCEL EDA provides versatility and extensive functionality in a logical, easy-to-use manner. We think you'll be pleased with the results.

In this Guide we've highlighted the user interface, basic editing commands, and some advanced design features. Should you wish to explore further, check the on-line help with hypertext cross-references and search facility.

The bottom line for measuring the worth of electronic design tools is whether they enable you to create quality designs in less time -- in other words, do they make you *more productive*? We're confident ACCEL EDA does the job. And by testing the software in this evaluation package, you can judge for yourself. So without further commercial interruption, here's ACCEL EDA.

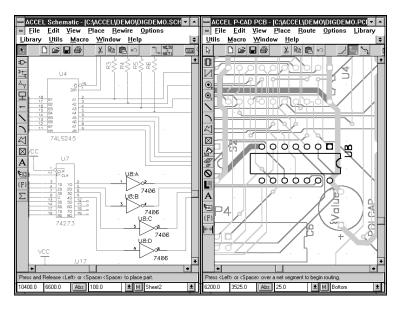

### The ACCEL EDA system

ACCEL EDA for Windows is a complete printed circuit board design tool suite with the following components:

- ACCEL Schematic: ACCEL Schematic is an advanced schematic-entry program. It seamlessly interfaces ACCEL EDA's PCB applications, sharing component libraries, passing net and component data forward, and receiving ECO data back from the PCB layout program.

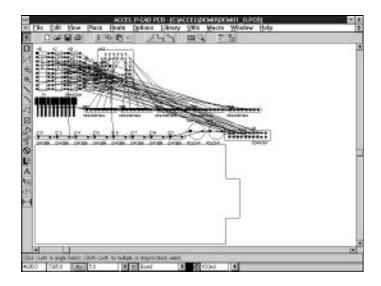

- ACCEL P-CAD PCB: ACCEL P-CAD PCB is the design editor within which components are placed, connections are made, routing is completed, design rule checking is performed, and artwork and CAM files are generated. Includes a built-in maze autorouter, QuickRoute, and an interactive shape-based routing tool, InterRoute.

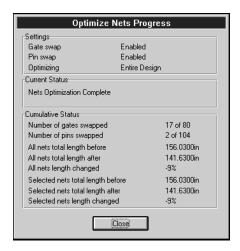

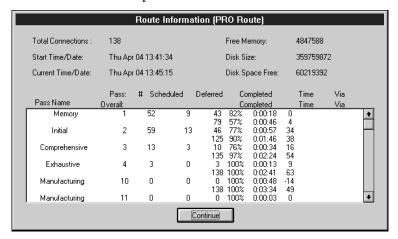

- ACCEL PRO Route: ACCEL PRO Route is an optional, high-completion, rip-up and reconstruct autorouting engine that operates seamlessly from within ACCEL P-CAD PCB.

- ACCEL Library Manager: ACCEL Library Manager is used to manage the symbolic, physical, and electrical data of ACCEL EDA's integrated components. It is supplied with ACCEL Schematic and ACCEL P-CAD PCB.

In addition, **ACCEL Tango PCB** is the reduced-function version of ACCEL P-CAD PCB, available to address the needs of 80% of all designers. Built with the same user-friendly, interface described in this guide, it is priced to be an exceptional value. **ACCEL PRO Route 2/4** is a reduced-priced version of ACCEL PRO Route for designs with up to 4 signal layers and 4000 pins, or those having only 2 signal layers (no pin limit).

ACCEL also offers high-end **SPECCTRA** autorouters, the **CAM350** Family of CAM tools, an interface to **Viewlogic** engineering tools, floating network licenses, an application programming interface (API), and several translators to meet your special needs for designing today's PC boards.

Together, ACCEL EDA applications provide the flexibility and power needed to meet your most challenging design requirements.

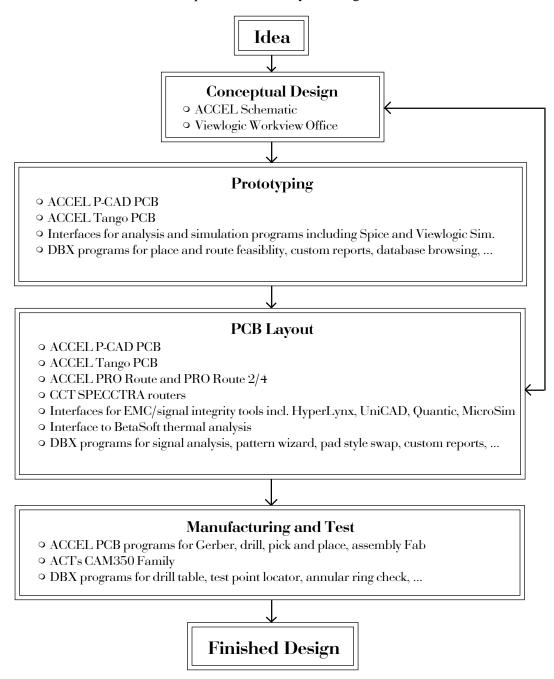

From concept through finished board, ACCEL EDA offers a complete solution for your design needs:

#### **Evaluation version limitations**

The software included with this evaluation package is the real thing with these exceptions:

- Design work cannot be saved or copied to a file.

- You can only generate output (specifically prints, plots, photoplots, schematic netlists, and DXF) for files that have not been edited with the eval version.

- Database exchange (DBX) functions are disabled.

- Cut and copy functions are disabled.

- For routing, ACCEL PRO Route checkpointing is disabled and you cannot save the output or restart that router. You cannot edit or save SPECCTRA Do-Files or start the SPECCTRA autorouter.

- A subset of library components is distributed and some sample files are missing. Additional files can be accessed by calling either of our bulletin board systems at 619 554-1018 or 408 271-1413 and downloading PRODEMOS.ZIP. Settings are automatically detected.

- The eval is unsecured and may be freely copied.

Otherwise, you have access to the functionality in the full ACCEL EDA package. We encourage you to try out as many features as time permits.

### Using this guide

This guide leads you through installation and evaluation of the ACCEL EDA product line including schematic, PCB, and routing applications. Most of you will benefit by going through the entire document in order. However, if you are interested in reviewing only one or two of these products, or already own ACCEL EDA, you can save time by referring to the relevant sections:

If you're not already an ACCEL EDA user, you'll want to go through Sections 2 and 3 to learn the fundamentals of the ACCEL EDA family of products. We've kept the user interface information generic so either ACCEL Schematic or ACCEL P-CAD PCB can be used to follow along. ACCEL EDA users can bypass these sections; the basics don't have to be relearned because the interfaces are so similar!

Following the basics, Sections 4, 5, and 6 focus on Schematic entry, PCB design, and autorouting, respectively. You can head directly to the sections that pertain to your interests and skip the others. Linking the Pieces is covered in Section 7 and is of interest to both Schematic and PCB designers.

The final section, *Taking the Next Step*, is for everyone. It concludes the evaluation and directs you toward the next step.

Let's get started!

## Installation and Setup

This section covers the required hardware and software necessary for installation, and shows you how to install the ACCEL EDA programs.

We assume you are already familiar with the basic layout and operations of Windows.

### System requirements

Be sure that your PC (or compatible) and its software conform to the following ACCEL EDA requirements and recommendations.

- A 486 or later processor running at least at a 33 MHz clock speed is required; 66 MHz or more is recommended.

- Microsoft Windows V3.x, Windows 95, or Windows NT operating system.

- 8 MB of RAM is required, 16 MB or more is recommended (16 MB is required for autorouting).

- CD-ROM drive.

- A hard disk is required. Space used depends on programs installed and is indicated during the installation procedure.

- A Microsoft (or compatible) mouse is required.

- A VGA (or better) graphics card is required. Color is recommended.

- *share.exe* must be loaded to run the Library Manager under Windows 3.x. See your Windows manual for information on installing it from within your *autoexec.bat* file.

### Installing ACCEL EDA

- 1. Start Windows and display the Program Manager utility.

- 2. Insert the ACCEL EDA evaluation CD into your disk drive.

- 3. From the Program Manager in Windows 3.x or NT, select Run from the File menu to display the Run dialog box

or

if you are using Windows 95, choose the Run command after selecting the Start button.

4. In the edit box, type

d:\setup,

where d: represents your CD drive letter. Click **OK**. The ACCEL EDA installation utility will begin. Just follow the on-screen instructions.

New users should at least install ACCEL Schematic or ACCEL P-CAD PCB since either can be used to learn the program fundamentals presented in Sections 3 and 4. ACCEL Schematic, ACCEL P-CAD PCB, or the Library Manager may be installed alone or in any combination. However, because autorouting is invoked as a PCB command, you must install both ACCEL P-CAD PCB and ACCEL PRO Route to evaluate the autorouter.

Using the eval as a second print/plot station The ACCEL EDA eval can be used as a second, unkeyed print or plot station to complement your full copy of ACCEL EDA. Just load any design saved in the full version and generate the desired output. Note however, that the eval's output functions become disabled if any edits are made to the design using the eval.

Note to ACCEL EDA users

If you are already an ACCEL EDA user and are installing this software to evaluate another application or to use it as a second output station, be sure to install the eval in a directory other than where your full copy of ACCEL EDA resides. Otherwise, the installation will overwrite your production copy of the program. By default, the evaluation is installed in a separate directory.

If you own ACCEL P-CAD PCB and want to evaluate the autorouter, you must install the evaluation versions of both applications. The eval version of ACCEL PRO Route will *not* operate with the full version of ACCEL P-CAD PCB.

## ACCEL EDA Basics

In this section, we'll introduce you to ACCEL EDA's user interface and some of the options for customizing the program for your own use. The ACCEL Schematic and PCB interfaces are so similar that you may use either program to follow along.

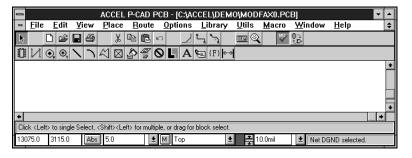

### The ACCEL EDA interface

After starting ACCEL Schematic or ACCEL P-CAD PCB you'll notice that the screen shows a combination of standard Windows features together with unique ACCEL EDA features. You'll find application-specific differences between ACCEL Schematic and ACCEL P-CAD PCB (like the tools offered in the Toolbar), but the screens are otherwise the same.

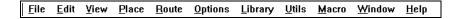

### Menu bar

To activate a menu command, click on the menu title or press the *Alt* key in combination with the underlined letter of the title (e.g., *Alt+F* to display the File menu). When the menu is displayed, click on the menu item or press the underlined key to enable a command. The PCB menu is shown below; the Schematic menu includes the Rewire command instead of Route.

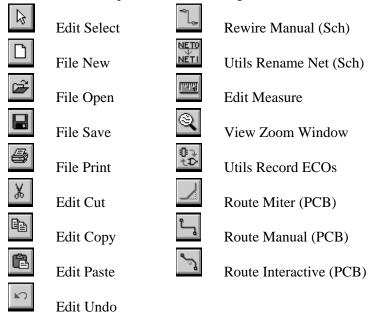

#### Command Toolbar

The Command Toolbar consists of graphical buttons displayed just below the menu bar or on either side of the screen, according to a setting in the Options Preferences command. These provide direct access to menu commands and other system functions. The Schematic and PCB Command Toolbars follow. See your ACCEL Schematic and ACCEL P-CAD PCB Quick Reference Guides for more details.

The buttons correspond to the following actions:

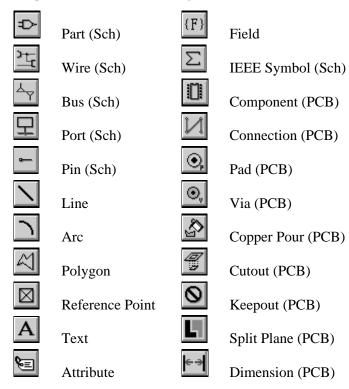

### Placement Toolbar

The Placement Toolbar provides shortcut access to ACCEL EDA's placement commands. Using the Options Preferences command, you can locate this Toolbar vertically on the left or right of your display or horizontally below the Command Toolbar. The Schematic and PCB Placement Toolbars follow:

See your ACCEL Schematic and ACCEL P-CAD PCB Quick Reference Guides for more details. The buttons correspond to the placement of the following items:

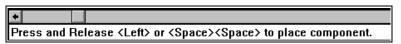

#### Prompt line

The Prompt line lies below the work area and scroll bar, extending the width of the ACCEL EDA display. When there is no prompt, the area is empty.

#### Status line

The Status line features are as follows, from left to right:

- X and Y coordinate edit boxes

- grid toggle button, edit box, and select button

- default macro record button

- schematic sheet or PCB layer combo box, select button, color block (click it to quickly access the Options Sheet or Options Layer dialog box), and scroll buttons

- line width edit box and select button

- Status line information area

A new X and Y coordinate, grid, and line width can be set by typing into the corresponding edit boxes. This is a speedy way to get to an exact location or create a new grid or line width.

# Keyboard basics

ACCEL EDA also supports keyboard operations, including shortcut keys, to speed editing for those leery of electronic rodents. The ACCEL EDA keyboard shortcuts are listed on the Quick Reference Guides provided with this evaluation. You can also place objects using only the keyboard. The following are keyboard equivalents of actions, otherwise performed with the mouse:

Access the menu: Press Alt and the underlined letter

shown on the menu bar

Execute a command: Choose the underlined letter for

the command

Dialog box operations: Press the *Tab* key to cycle through

dialog controls; *arrow* keys to move within a control; and the *spacebar* to make a selection

Move cursor 1 grid point: Press the *arrow* keys

Move cursor 10 grid points: Press the *Ctrl+arrow* keys

Mouse down (click): Press *spacebar* once

Mouse down and up: Press *spacebar* twice

(click and release)

Terminate a command: Press *Esc*

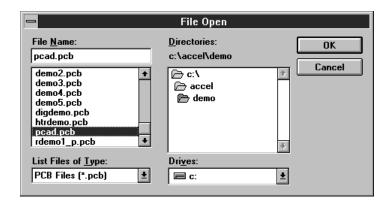

### Loading a file

Like most Windows applications, the File New command starts a new design and File Open is for loading an existing file. You can also read Tango-Schematic and Tango-PCB PLUS designs directly into ACCEL EDA once your DOS libraries are translated using the Library Manager's Library Translate command.

# drag and drop file loading

As an alternative to File Open, save time with the *drag and drop* method of loading a file. Using Windows File Manager, click on the filename icon of a design file in the eval's Demo subdirectory (e.g., c:\acceval\demo\digdemo.sch for Schematic, or c:\acceval\demo\accsampl.pcb for PCB), drag it into the ACCEL EDA window, and release to drop it. The design file will open. This handy method works to open design files (.SCH or .PCB), library files (.LIB), and netlist files (.NET).

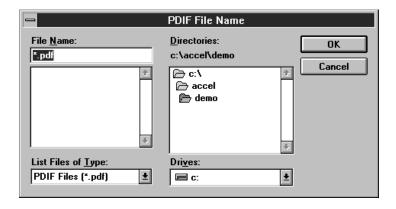

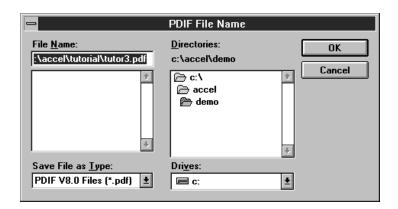

# working with PDIF files

P-CAD binary or PDIF files can be imported using the File Open and File PDIF In commands respectively. For more details see Appendix A, Using P-CAD Files.

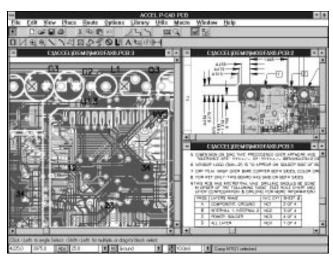

## Multiple document interface (MDI)

ACCEL EDA has a built-in Multiple Document Interface (MDI) capability for maximum flexibility in viewing your designs.

- 1. Open an additional file. To open a new view of the current file, choose the Window New Window command. Notice that all of your open windows are listed at the bottom of the Windows pull-down menu. You can set any window to be the current window by choosing it from this list.

- 2. Cascade the open windows by using Window Cascade. Use the standard Windows interface to move, resize, minimize, maximize, close, or make any of them current.

- 3. Next run Window Tile to set up for viewing the windows.

MDI lets you view multiple designs at the same time cut/copy/paste between them for fast editing (retail version only)

#### Zoom commands

Zooming comes in handy while placing components, routing connections, or otherwise working close-up on your design. ACCEL EDA offers several options for controlling how much of the design you see and what parts are visible.

### (View) Zoom In/Out

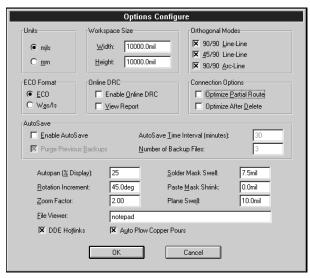

Move the cursor to any area on the sample board that interests you and choose the View Zoom In and View Zoom Out commands from the menu, or press the *plus* (+) key to zoom in and the *minus* (-) key to zoom out. The **Zoom Factor** value in the Options Configure dialog determines how much the display is changed. Use Options Configure to modify this value and try zooming again.

#### (View) Zoom Window

With the Zoom Window command, you can zoom in on any area on the workspace you choose. Invoke Zoom Window with the Z key, the Toolbar zoom button, or the View Zoom Window menu command. Click and drag the cursor to define a viewing window. Release the button and the window you designated will fill the workspace.

# other View options

You may want to experiment with a number of the other options available on the View menu, such as View Center (the *C* key) and View Extent. These will respectively center the cursor location and cause the display to encompass all items in the workspace. You can pan across the workspace by repeatedly moving the cursor and pressing *C*. When using *arrow* keys, the screen automatically pans when moving your cursor to the screen's edge. The screen is shifted by the **Autopan (% Display)** amount set in Options Configure. Toggle between the last two "views" of the design by using the View Last command. And, the entire workspace becomes visible with View All.

### Customized shortcut keys

Choose the Options Preferences command and take a look at how much control you have over configuring your keyboard shortcuts. Keys, including those you just used for zooming, can be assigned to menu commands, many special actions, and macros. ACCEL EDA ships with default settings which can be modified to match your preferences. We'll assign the Redraw command to a function key. Here's how:

With the **Menu commands** radio button selected, choose View Redraw from the combo box on the left. Click in the **Press a Shortcut Key** box and press the *F1* key on the keyboard. A message displayed below the shortcut box indicates the key is already assigned: *Current Binding: Help Contents*. Assigning *F1* to Redraw would delete the current assignment. Instead, press *F3* (which has no other assignment) and click the **Assign** button to bind *F3* to the command

Preferences are saved in a key file that can be recalled at any time by pressing the **Key File** button and entering the file name. This allows settings to be shared or carried to other machines.

## Complete Imperial and metric support

ACCEL EDA supports both metric and Imperial units, and accurate conversion between them. To set your global design units or change them at any time, choose Options Configure and select mils, millimeters, or (in Schematic only) inches in the **Units** box. Click on the **mils** and **mm** buttons, and notice how the size of the workspace is automatically converted.

ACCEL EDA intelligently handles units of measure. All data throughout the system is presented in the chosen global units, and any data you input is assumed to be in those design units. However, you can always override the units by appending a suffix (with no space) to the value; **mm** for millimeters, **mil** for mils, **in** for inches. For example, if your design units are millimeters, you might specify 100mil in a dialog box. This value would be converted to 2.54 millimeters and then displayed in the box.

measurement tool

To measure distances in your design, choose Edit Measure from the menu or click on the Toolbar button. Click on the starting point and as you move the cursor, the x, y, and total distances are provided on the Status line.

ACCEL EDA's 32-bit database precision assures absolute accuracy whether using Imperial or metric units.

### **Styles**

The concept of using styles in software is not unique, but it does require some explanation. A *style*, as defined for use in ACCEL EDA, is a named combination of settings that define the properties of a specific object. Let's use an analogy.

For dairy farmers, the Holstein Friesian *style* of cow is white with black spots and a prolific producer of medium-fat milk. Guernseys, on the other hand, are brown and white, and produce very rich milk in lesser quantities. The *style* describes the characteristic properties of the cow. If a farmer wants to introduce Brown Swiss cows into the herd, a new style ("Brown Swiss") is needed to describe all of the cows owned by the farmer. Many individual cows are described by a single style.

styles are applied to any number of similar objects Likewise, ACCEL EDA uses styles for text, pads, and vias. You create a named style the first time you need a particular combination of properties. After the style is created, it becomes available to apply to any number of similar objects.

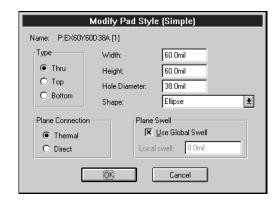

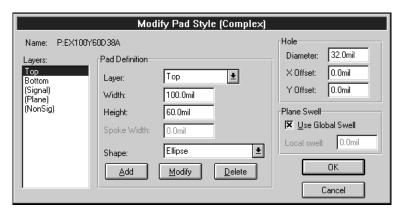

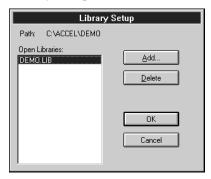

For text, the properties include height, thickness, and font. Pad and via styles define the shape and size of pads on each layer, drill hole information, and data about the plane swell.

When creating a new item, the *current* style is used to define the item's properties. Once placed, an object can be modified to have a different style. For your convenience, default styles are provided and used unless a different one is set to be current.

using styles simplifies global editing

Except for pre-defined styles, styles themselves can be redefined. This powerful feature must be used with caution. Changing a style's properties affects each object using the style!

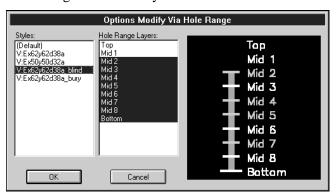

Styles are created, modified, deleted, and set current in the Options (Text/ Pad/ Via) Style commands. You'll get a chance to use pad and via styles in the PCB Design Session.

## Setting grids

Whether you are running ACCEL Schematic, PCB, or Route, correct grid spacing is important for placing objects in your design.

Use the Options Grids command to set the current grid for your particular requirements; perhaps 2.54 mm spacing for easy

ACCEL EDA Evaluation Guide Section 2 - ACCEL EDA Basics

alignment of your metric Schematic symbols, or 50 mils for placing your surface mount PCB components, as follows:

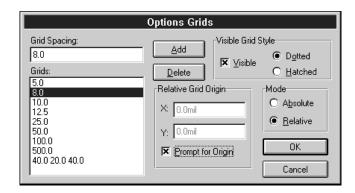

To set a new current grid, choose **Absolute** Mode, then select a grid from the **Grids** list and click **OK**. If the desired spacing is not shown, type a new value in the **Grid Spacing** box and click **Add**. The Status line reflects the change.

You can also set or change the settings for relative grid mode. Whereas the absolute grid origin is always the bottom left hand corner of the workspace, the relative grid origin can be located anywhere. A relative grid is particularly useful for locating objects in relation to a datum point.

We've already mentioned you can also toggle the grid mode and select or add a new grid spacing directly from the Status line. Although direct access will probably become your preferred method of grid selection, the Options Grids command dialog box includes some additional features.

select relative or absolute grids for placement and routing with the Options Grids command

Notice you can also control the grid visibility and style, delete a grid, and define the relative origin from within the dialog.

### Component libraries

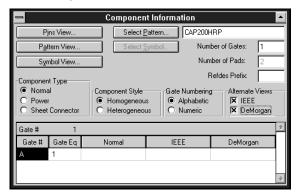

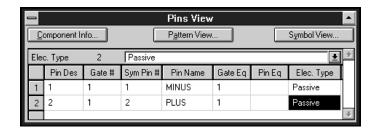

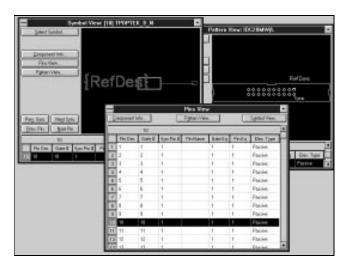

In ACCEL EDA, a component is a collection of data including electrical information (e.g., pin designator, pin name, swapability), a symbol for use in Schematic, and a pattern for use in PCB. The ACCEL Library Manager manages and integrates component data for use by both Schematic and PCB.

Thousands of components are organized into libraries and shipped with the software. As described in Section 7 of this guide, you can also create your own custom components.

We won't go into detail on this now, other than to say that parts in Schematic and components in PCB are placed from libraries, and libraries must be opened prior to placement.

# section review

In this section we have shown you:

- The ACCEL EDA user interface, including a tour of the screen, menus, and keyboard operations.

- How to load files.

- How to display multiple views of multiple designs.

- The various zoom options for viewing the workspace.

- How to customize your keyboard for taking shortcuts.

- How to mix Imperial and metric data.

- How styles are used.

- How to set up grids.

- Component libraries.

We'll now move on to cover the basics of placing, selecting, moving, changing, and deleting objects in a design.

# Placing, Selecting, and Editing Objects

This section introduces you to the ease of placing, selecting, moving, and modifying objects in ACCEL EDA.

# why it's so easy to use

ACCEL EDA was designed with your efficiency in mind. You can place objects directly from the Toolbar without extra key strokes or mouse clicks. Then, when you need to move, edit, or delete any combination of objects, select them and do it!

Pop-up menus, keyboard shortcuts, context sensitive editing, and the editable Status line all contribute to letting you concentrate on your work without wasting time weaving through commands.

## Placing objects in ACCEL EDA

*Place* commands allow you to either draw new objects or place already created objects, such as components, into your design.

The items that can be placed in your design are those listed in the Place menu. Objects common to Schematic and PCB are Line, Arc, Polygon, Text, Attribute, and Field. In ACCEL Schematic you can also place a Part, Wire, Bus, Port, Pin, Ref Point, and IEEE Symbol; and using ACCEL P-CAD PCB you can place a Component, Connection, Pad, Via, Point, Copper Pour, Cutout, Keepout, Split Plane, and Dimension.

All objects can also be placed using the Placement Toolbar. Icons are in the same order as listed in the Place menu. Toolbar visibility is controlled with the View Placement Toolbar command. Choose the **Toolbars** tab within the Options Preferences dialog box to display the Toolbar along the top or either side of your design.

# options during placement

During placement, certain actions are available depending on the type of object being placed. These include zooming, moving, rotating, and flipping objects (e.g., text, parts, pins, pads, ports, components), *unwinding* segmented objects (e.g., polygons, lines, copper pours, split planes, wires, buses, manual routes), and changing the center point of an arc before placement is final.

undo

There's no need to worry if you goof during placement, or while performing just about any other action for that matter, because ACCEL EDA comes with Undo. Your last operation is undone in a single step by selecting the Edit Undo command, clicking the Undo Toolbar icon, or pressing the *U* key. It's that easy!

Undo saves the day!

ACCEL EDA supports one level of undo. Placements, deletions, and modifications can all be undone, and you can even undo an undo. (Many other programs only support *undelete*; check specs carefully!)

# hands-on practice

The following are some simple step-by-step exercises in placing various objects, using some of the placement options. Since ACCEL Schematic and ACCEL P-CAD PCB operate the same way, you can use either application to practice.

If ACCEL EDA is not already running, start either ACCEL Schematic or ACCEL P-CAD PCB by double clicking the application's icon. Otherwise, use File New to start a new design. In either case, maximize the window to fill the workspace. Zoom in a bit and try the following placement exercises.

exercise #1: placing lines

Lines are non-electrical entities, used for creating board outlines, symbols and patterns, and annotating your designs.

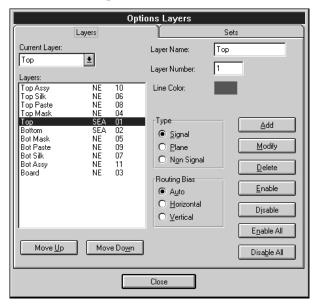

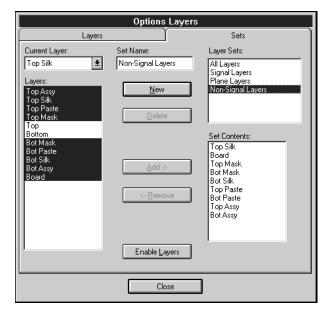

- First create a new sheet or layer. Choose Options Sheet (Schematic) or Options Layer (PCB). Enter a new name and, for PCB only, a new number, type, and bias. Then choose Add. Notice your new entry is added to the list box. Make it current by choosing the Current button or Current Layer combo box, and then close the dialog.

- Practice switching between existing sheets or layers using the Select and Scroll buttons on the Status line.

- To add lines, choose the Place Line command from the Toolbar, menu, or keyboard and move the cursor into the workspace. Click, drag, and release to draw the first segment; repeat the action (or position and click) to draw

two or three more segments. Terminate line creation by pressing *Esc* or the right mouse button.

change line settings during placement 3. Use Options Current Line to change the default line width or style. Alternately change the width by typing directly into the width edit box on the Status line or choosing from the Status line's width combo box. Start your next line; just click and drag in the workspace. Subsequent lines are created with the new setting. The width can be changed after any segment is placed, before terminating the line.

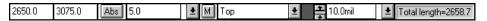

line length is dynamically calculated and displayed on the status line

4. Watch the Status line information area (lower right corner of the screen) as you draw line segments; the delta-X and -Y measurements are given while you drag a segment, and the total line length is given when you complete each segment.

orthogonal modes make placing complex lines easy

5. ACCEL EDA supports several orthogonal modes. While drawing a diagonal line segment (and before the left mouse button is released), press the *O* key to toggle through the options. Once you get to the orthogonal shape you like, press the *F* key to flip the line. In PCB, the arc is only supported for manual routing, not for placing lines. Enable and disable modes using the Options Configure command.

unwind unwanted line segments during placement 6. Before completing the line, press the *backspace* (unwind) key ←, and the previous segment disappears. Add or unwind more segments, then complete the series of segments with a right click. For practice, press *U* once to undo the entire line, and again to bring it back.

exercise #2: placing arcs and circles

The Options Current Line command is used to establish the width setting for arcs. You should also note that in PCB arcs differ from current-carrying curved tracks which are created while routing with the Route Manual tool.

Arcs are constructed counter-clockwise; an initial click (down), drag, and release (up) define the start and end points of the arc. A second click and drag allows you to move the center point, effectively changing the arc's radius and sweep angle.

To create a full circle, the first click and release should be at the same point (with no drag), along the X-axis of the desired circle. The circle's center point is then defined by clicking a second time and dragging the mouse horizontally.

- 1. Choose the Place Arc Toolbar button or menu command.

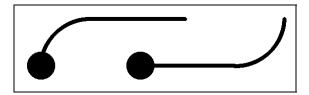

- 2. Move the cursor to a grid point in your workspace. Click and drag the mouse at a 45-degree angle towards the upper right of the workspace, then release. The unfinished arc should look like **a** in the diagram below. Press the *F* key to see how to flip the arc. Press it again to return to **a**.

- 3. Click over the center point and drag it towards the upper left to form a 90-degree corner as shown in **b**. Release and notice that you have created a 90-degree arc, like **c**:

4. Create a circle by clicking and releasing without dragging the mouse. Click a second time and drag to the right and left to see how the size of the circle changes.

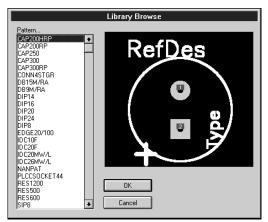

exercise #3: placing parts and components

Schematic part symbols and PCB component patterns are placed similarly, from an integrated library. ACCEL EDA's libraries contain information for both applications.

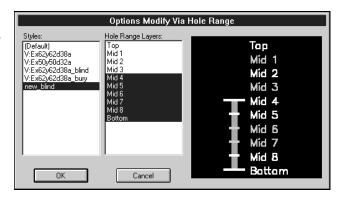

1. Choose the Library Setup command to open a library. Click **Add** and select DEMO.LIB from the eval's Demo subdirectory, then close the dialog box by clicking **OK**.

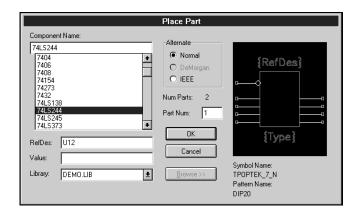

- Choose Place Part (Schematic) or Place Component (PCB) from the Toolbar or menu. Click left in the workspace. A dialog box lists available components or parts. Choose Browse to view each item graphically (only displayed if a symbol or pattern is defined for the component).

- 3. Scroll through and click on any name listed in the box. Specify a **RefDes** if desired, and click **OK**. Then click left in the workspace and *hold* down the mouse button.

browse library parts prior to placing them in ACCEL Schematic

a single keystroke rotates or flips parts and components during placement 4. While holding the button down, press *R* to rotate the item 90 degrees counterclockwise. In the PCB Design Session section you'll learn how to rotate to other angles. Press *F* to flip the object and, finally, release the mouse to place it.

Each new click places another object of the same type and orientation. It can be moved, rotated, and flipped as well. The Status Line shows the RefDes being assigned. Press *D* before placing another object to increase the RefDes; *Shift+D* to decrease it. In Schematic, *P* increases the part number on multi-part packages; *Shift+P* decreases it.

The *Esc* key or right button ends the placement of a particular object. Click the left button again to display the dialog, and select a different part or component to place.

exercise #4: try placing some other objects Now let's try placing some of the remaining objects, briefly described below. All are accessible from the Toolbar, Place menu, or keyboard. Follow the Prompt line and remember to use the Help command for more information. Also, recall that the *F* and *R* keys will flip and rotate many objects during placement. In PCB, objects can be rotated to 0.1 degree precision.

The following objects can be placed in both Schematic and PCB:

The Ref Point command in ACCEL Schematic is used for placing reference points when you are creating new symbols. Click the left mouse button, drag to the desired location, and release to place the point. **Point** is the corresponding command in PCB. Use it to place reference points, glue dots, and pick-and-place points on new patterns as you create them.

• A **Polygon** is a filled, multi-sided entity. Create one the same way you created the multi-segment line. The polygon is filled when the *Esc* or right mouse button is pressed.

• **Text** is free text in a design. Click in the workspace to view the dialog box for assigning text, orientation, and style.

• An **Attribute** is an entity with an assigned value placed globally or as part of a component, part, or net. To place a global attribute, click in the workspace. Other attributes are accessed through the Properties dialogs (double click a net, part, or component). Select a category and pre-defined attribute name from the list boxes or enter a new user-defined name. Add a value or leave it blank to be entered later. All attributes and their values can be set in the schematic and transferred to the PCB via the netlist.

• A Field is an item that is updated automatically by ACCEL EDA. The Current Date, Current Time, Number Of Sheets, Current Sheet, and Filename fields are maintained by ACCEL EDA. Values for Author, Date, Time, Revision, and Title fields are taken from the File Design Info command dialog box. Add a few of these fields, then update the data using Design Info. Redraw the screen to see the new values.

Several more objects can be placed in ACCEL Schematic:

• A **Bus** is an electrical item used to carry multiple signals. It is placed like a line. When a wire is placed to start or end on a bus, the net is automatically assigned to the bus and the connection is graphically displayed with a bus entry.

• A Wire is an electrical item that defines net connectivity. Place wires like lines, starting and ending on pins, buses, or other wires. Watch the Status line during placement. Default net names are automatically assigned. We'll show you later how to reassign them. A junction is automatically added when a wire starts or ends on another wire. Junction size and the display of unconnected ends are controlled in the Miscellaneous box in Options Display.

• A **Port** identifies subnets of logically, but not physically, connecting portions of a single net. Click in the workspace to bring up the dialog for selecting net name and display options. Then click and drag to locate the port on a wire.

• A **Pin** is the part of a symbol used for connecting wires. Use the Place Pin command to place pins during part creation. Click in the workspace and choose the pin characteristics. Click and drag to locate the pin.

An IEEE Symbol is placed by choosing this command and clicking in the workspace. Adder, Amplifier, Astable,

Complex, Generator, Hysteresis, and Multiplier symbols are available. Symbol size is controlled within the dialog.

These objects are specific to ACCEL P-CAD PCB:

• Place a **Pad** or **Via** freely on the board or as part of a library component pattern. Set the desired style in Options Pad (or Via) Style, then use Place Pad or Place Via. Click and drag, then release, to locate the object in the workspace.

• The **Copper Pour** is a solid or hatch-filled polygon placed on a signal layer, with user-defined backoff from all other entities in the area. It can be attached to a net. Pours are often used for shielding. (Wait to try this one, because we'll take a close look at it in the PCB Design Session.)

• A **Cutout** is an area defined within a copper pour that is void of copper. It is placed just like a polygon.

• The **Keepout** (PCB and Route) defines a line or polygon across which the autorouter will not route. The Options Current Keepout dialog is the place you choose the type of keepout and define it for one or all layers. Create keepouts just as you create lines and polygons.

• A **Connection** defines electrical connectivity between two pads. Click on a component pad, drag to another pad in the same net, and release. Nets can be defined in this way.

• A Split **Plane** divides a power or ground plane to allow for multiple net assignments. Splits are created as polygonal areas. Details are provided in the PCB Design Session.

A Dimension is added to annotate the design for manufacturing. Choose this command and click on a line or arc to be dimensioned. Point-to-point, baseline, diameter, center, leader, radial, and angular dimensions are supported.

## Selecting objects for action

ACCEL EDA's select tool is the most powerful in the business We're proud of ACCEL EDA's placement commands and the options, functionality, and interface we provide for creating designs. But it's the strength of ACCEL EDA's "select-edit" methodology that really sets us apart and allows you to complete designs in a more effective manner. When you're ready to move, copy, modify, resize, delete, highlight, or otherwise operate on any part of your design, you simply select objects and do it.

#### selection methods

A variety of methods are offered to efficiently isolate *exactly* those items you wish to edit. Let's cover these before jumping to the great things you can do with the selected items!

Choose the Select tool from the Toolbar or Edit menu, or by pressing the *S* key. When an object is selected, its display changes to the Selection color set in the Options Display dialog.

the status line identifies selected items

The Status line information area identifies selected items, either specifically (e.g., part #) or generally (e.g., # of items selected).

#### Part U1:A selected.

Zooming can be performed while you are selecting objects, just like during placement. Try pressing the Z (View Zoom Window), C (View Zoom Center), + (View Zoom In), and - (View Zoom Out) keys to adjust your view during selection.

• **single select.** In Select mode, click over a single object to select it. If items are collocated (on top of each other), click at the same location to toggle through the items until the one you want is highlighted.

In ACCEL P-CAD PCB, Select is layer-specific. If an item is on a specific layer, then that layer must be current to allow selection. Change the current layer using the Status line layer Select or Scroll buttons. Some items, such as through-hole pads and components, exist on all layers.

it's simple to add to, and delete from, a selection

• **multiple select.** Add items to the selection by holding down the *Ctrl* key and clicking on the additional items. Remove an object from the selection by pressing *Ctrl*+click on it a second time. Use this in conjunction with other selection methods to update the selection list at any time.

Add collocated items to a multiple selection by clicking at the same location to toggle through items until the one you want is added to the selection.

#### Note:

The Ctrl and Shift keys used to extend a selection or to subselect items can be reversed. Locate this option by selecting the Mouse tab within the Options Preferences command.

sub-selection gives you editing access to the individual parts of an item

- **sub-select.** Select a portion of an item by holding down the *Shift* key (see note above) and clicking on a sub-item. Try selecting a component pad or pin, a net name, or RefDes.

- **block select.** To select a block of items, click and drag to create a *selection box* to surround the desired objects.

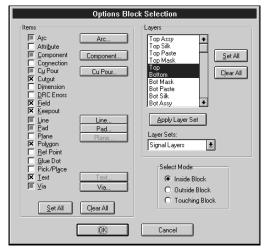

Block selections are extremely powerful because of the variety of ways you can include or exclude specific types of objects in the selection. This filtering is controlled from the Options Block Selection dialog. Add several text strings using different text justifications and styles to your design. We will select them using the filter.

control the type of objects being selected

Choose Options Block Selection. Checkboxes are available for every object that can be placed. Clearing an object's checkbox excludes that object type from being block selected. Checking the box includes the object type.

perform editing operations on the items of your choice with the block selection filter

Try selecting all text on your current Schematic sheet or PCB design. Click the **Clear All** button and then enable only the **Text** checkbox. In PCB, click **Set All** to enable all layers;

block selection looks for items only on enabled layers. Choose the **Outside Block** radio button then click **OK**. Click and drag to define a small selection box, making sure you avoid all text. Practice choosing items inside a block, outside a block, or touching a block.

be specific in your selection

Selection of objects with an associated push button (e.g., arcs, lines, text) can be more specifically defined. Try this for text. Choose Options Block Selection again. This time toggle the **Text** checkbox to be gray, which enables the **Text** push button. Click this push button. Set the Text Selection Mask to match some text in your design, then block select only that text. Try again by specifying different justifications or styles. **Remember to reset your block selection options before trying to block select other objects!**

a single command finds all items in a net

- **select net.** Place a few wires or connections in your design and try selecting an entire net (use the Place add to add parts or components, then again to add the wires or connections). Select one item in the net, click right, and choose **Select Net** from the pop-up menu. The entire net will be selected.

- edit nets. Use the Edit Nets command to select nets by their name. Choose one or more net names from the list box and then click the Select button.

- select nets by node count. To select nets with a given number of nodes, choose the Edit Nets command from the menu, or select a net and pick the command from the right mouse pop-up menu. Enter the desired Min: and Max: node count, then press the Set Net By Node Count push button. All nets with the correct number of nodes will be highlighted in the list box. Press the Select button and these nets will be selected (it will be grayed if no nets match the node count).

- **select contiguous.** (Schematic only) In the Schematic Design Session we'll show you how to create wires that are not physically connected, but carry the same signal. This is important for global nets such as power or clock lines. To choose only the physically connected wires (i.e., a sub-net), the **Select Contiguous** option is available from the right mouse pop-up menu when a wire is selected. We'll try this out later.

• **select all.** Use Edit Select All to select all items on a Schematic sheet or in a PCB design.

## restart the selection list by deselecting

- **deselect.** Click on an empty area to deselect all items. You are still in Select mode, but no objects are selected.

- deselect all. Use Edit Deselect All as an alternate way to deselect all items.

## Editing actions on selected objects

You are now ready to operate! Actions on selected objects can include the following, but depend on the type of item selected:

- delete

- move

- rotate and flip

- resize

- cut, copy, and paste

- modify

- obtain net information

- duplicate in a matrix

- align parts or components

- move by reference designator

- move to layer (PCB only)

- explode or alter parts and components

- cross probe between applications

Except for the last three items, we'll briefly examine each of these operations here. Feel free to explore more on your own.

right-button is the shortcut to editing selected items The right mouse pop-up menu provides direct access to the most common commands performed on selected objects. The list is *context sensitive*, meaning the actions presented are appropriate for, and apply to, the selected objects. Here's the menu presented when a part or component is selected and the right mouse button is clicked.

context sensitive popup menus give direct access to common commands Properties...

Copy

Copy Matrix...

Cut

Delete Del

Explode

Highlight

Unhighlight

Highlight Attached Nets

Unhighlight Attached Nets

Align

Selection Point

delete

To delete selected objects, use the Edit Delete command, press the *Del* key, or click the right mouse button to bring up the handy pop-up menu, and select the **Delete** option.

move

After items are selected, move the objects by clicking within the selection box and dragging to the new location, then releasing. It's that easy... click, drag, and drop.

ACCEL EDA Tip

If you are concerned about the accuracy of moving items while holding down the left mouse button (or if you just have a lazy index finger), you can use the spacebar instead of the left mouse button, as follows:

- one stroke *spacebar* = mouse button down (for dragging)

- two strokes *spacebar* = mouse button down *and* up (click and release).

You can also use the *Alt* key to free your index finger. Press the *Alt* key, click the left mouse button, and release the *Alt* key; you can then move the object anywhere without having to keep the mouse button depressed.

rotate and flip Press *R* to rotate your selection 90 degrees counterclockwise. Connectivity of net items (e.g., wires, traces) is maintained. In the PCB Design Session, you'll see how to rotate by 0.1 degree. To flip your selection in the X direction (about the Y- axis), press *F*. That makes flipping an object easier than tipping a cow, and a whole lot safer!

**resize** Resize an object by picking one of its handles and dragging to stretch the object. Handles are the squares displayed when certain objects are selected singly.

resize handles on an arc make it easy to change the sweep angle

For example, after selecting an arc, pick one of its endpoint resize handles and drag it to change the sweep angle. To resize a polygon, grab any vertex handle and move it to a new location.

# cut, copy, and paste

For copying within the same design, you can use the shortcut *copy drag-and-drop*, which is available in this eval. Select one or more objects then *Ctrl*+click left over the selection and drag to where you want to place the copy. Release to fix the object(s) in the new location.

easily copy part of one design into another

Although this evaluation software does not support cutting from, and pasting to, the Windows clipboard, this valuable feature is available in the retail version of ACCEL EDA. It is particularly useful for copying from one design into another. Use the Windows standard accelerator keys (*Ctrl+X*, *Ctrl+C*, and *Ctrl+V*) or choose the commands from the Edit menu.

include pictures in your design documentation

Graphics are also cut or copied to the clipboard in bitmap form (Windows Metafile format) for pasting into other Windows programs. This feature facilitates design documentation.

# modify properties

Once an object is selected, its properties are easily modified. The changes allowed depend on the type of object selected.

What objects can be modified? *Everything except points and IEEE symbols*. Double click any of these items and an *object* Properties dialog is presented.

Alternately, select one or more objects, click the right mouse button, and choose **Properties.** If multiple items of the same type are selected, all boxes with unmatched values will be left blank or grayed in the Properties dialog. Enter updated information in the dialog box and click **OK**. All of the selected objects will uniformly take on the characteristics (e.g., values) you specified.

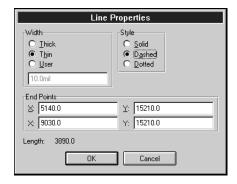

# modify line properties

The Line Properties dialog for Schematic is shown below. The line width, style and location can be modified. The PCB lines dialog is similar, but without a style option.

change the line width, style, and location in ACCEL Schematic

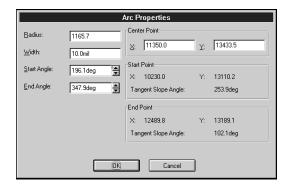

modify arc properties

The Arc Properties dialogs in Schematic and PCB are the same, giving you pinpoint control over an arc's radius, width, starting and ending angles, and center point.

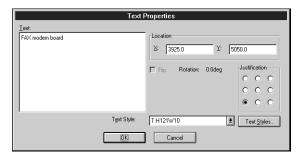

modify text properties

From the Text Properties dialog try changing the text contents, justification, and style of some placed text.

change text style, content or justification in the Text Properties dialog box

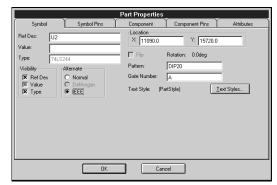

modify part and component properties The Properties dialogs for Schematic parts and PCB components allow you to update similar kinds of data. Try changing a RefDes and notice that the display is automatically updated. Additional options are discussed in the Schematic and PCB Design Sessions.

change characteristics of a part with the Part Properties dialog box

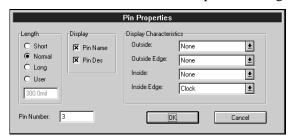

modify pin properties

Pins can be changed in a variety of ways using ACCEL Schematic, as seen in the Pin Properties dialog.

control pin properties from a single dialog

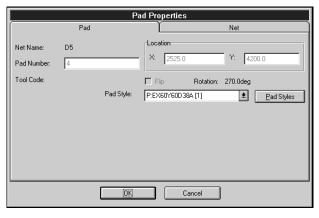

modify pad and via properties

The property dialogs are similar for PCB pads and vias. Select a new style or edit an existing one to modify these objects.

change a pad style in the Pad Properties dialog box

other changes

The visibility of net and bus names, and a port's type and net name are controlled from the Wire, Bus, and Port Properties Schematic dialogs. Also, we'll create and modify a copper pour, split plane, and dimension in the PCB Design Session.

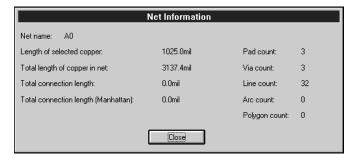

# net information

Display the net information of a net object (e.g., wire, via, trace) by selecting it, clicking the right mouse button, and choosing **Net Info** from the pop-up menu. The data provided differs between Schematic and PCB, but you access it the same way.

the Net Information box tells all about a given net in your PCB design

#### copy matrix

To quickly duplicate selected objects in the X and/or Y direction, use the Copy Matrix command. This command is particularly handy when creating new Schematic symbols or PCB patterns.

The following example shows how a 3 x 2 matrix of pads is easily created when starting with a selection of just one pad. Pins for a symbol can be duplicated in the same manner.

duplicate objects with Edit Copy Matrix

| Edit Copy Matrix   |          |  |  |  |

|--------------------|----------|--|--|--|

| Number of Columns: | 3        |  |  |  |

| Column Spacing:    | 200 OK   |  |  |  |

| Number of Rows:    | 2 Cancel |  |  |  |

| Row Spacing:       | 200      |  |  |  |

|                    |          |  |  |  |

duplication result

| 0 | 0 | ( |

|---|---|---|

|   |   |   |

#### alignment

With a single command, you can align placed components or parts vertically, horizontally, to a grid, or to be equally spaced. Select one or more items. Click the right mouse button and choose the **Selection Point** option from the pop-up menu. Press the left mouse and drag to locate a point of alignment. Then click right mouse again and choose **Align**. Set the desired options. Practice using the different options. Alignment onto the current grid can be done without choosing a selection point.

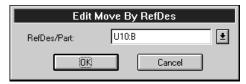

#### move by RefDes

ACCEL EDA comes with a speedy way to move a part or component if you know the item's reference designator. With the Select Tool active, choose the Move by RefDes command from the Edit menu. After picking the desired RefDes from the combo box, the part or component is selected and placed at the cursor location when you click the left mouse button. Recall you can enter exact cursor coordinates on the Status line and flip or rotate the item with the shortcut *F* and *R* keys.

### section review

In this section we have shown you how to:

- Place various objects in your design.

- Select objects using a variety of techniques.

- Edit, move, modify, delete, copy, and perform other operations on selected objects.

Now that you understand the basics of placing, selecting, moving, deleting, copying, and changing objects within ACCEL EDA, you are ready to design a simple Schematic or printed circuit board on your own. In the next section, we'll show you how to put it all together. You're well on your way to sophisticated board designs with ACCEL EDA.

### A Schematic Design Session

With basic ACCEL EDA concepts under your belt, you are now ready to step through ACCEL Schematic to create a small schematic design. Included in this design session, you will:

- 1. Set up your design preferences; workspace, display, title block, and libraries.

- 2. Create a simple schematic with parts, wires, buses, and ports.

- 3. Learn to work with your design; traverse sheets, locate and modify items, and obtain information.

- 4. Perform an electrical rules check.

- 5. Generate output; reports, netlist, and printed artwork.

### Setting up your design

# design configuration

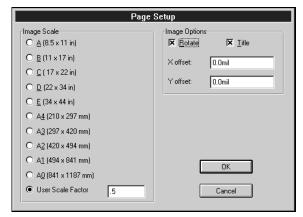

After starting ACCEL Schematic, choose the Options Configure command to set up your work area and operating options. For this design, an A-size drawing will be adequate. There's no need to fret over the sheet size decision; at any time just return to Options Configure and select another size. You can even change to a smaller sheet if all the schematic items fit in the smaller area.

Click **A** in the **Workspace Size** box. Notice the **Width**, **Height**, and title file, A.TTL, are automatically assigned. Click **Select** in the Titles box to locate the file in the eval's Titles subdirectory (e.g., c:\acceval\titles). Enable the **Display Title Sheet** checkbox to make the border visible.

Now is a good time to view the impact of switching units. Toggle between mils, mms, and inches, watching the **Width** and **Height** values change. ACCEL EDA's 32-bit database enables accurate conversion of all data. Set the **Units** to **mils**.

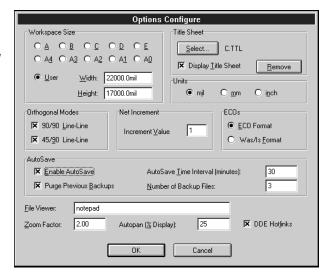

set your configuration options with the Options Configure command

Enable all **Orthogonal Modes**, **ECO Format**, and **DDE Hotlinks**, and set the **File Viewer**, **Autopan** (% **Display**), and **Zoom Factor** values to your preference. Notice this is the command used to set the AutoSave options in the retail product. Click **OK** to exit.

# display options

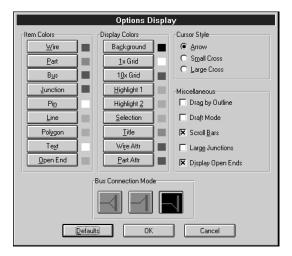

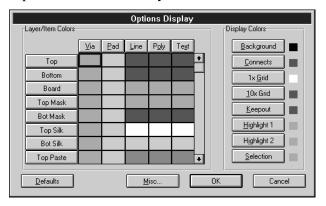

Setting your display and color options is done with Options Display. Choose this command from the menu or keyboard.

easily change colors and display options

To modify the color for an item, click the *item's* push button then choose a basic color from the palette. You can similarly control your background, highlight, grid, item selection, attribute, and

title colors. Before leaving the Options Display dialog, choose your preferred cursor style and bus connection mode, and enable the **Display Open Ends** option. Click **OK** to set your selections.

#### title block and fields

You can fill out your title block using fields. Fields reduce maintenance because each instance is updated automatically when the field's data changes.

add TrueType fonts to your design

Let's create a new TrueType font style to use. Choose the **Add** push button in the Options Text Style command dialog box.

Type a **Style Name** and click **OK**. Within the displayed Text Style Properties dialog, choose the **True Type Font** radio button, and then the **Font** push button. Select any **Font** with a **Size** of 12 (points). Return to your design by clicking **OK** or **Close** to exit the dialogs. Make the new style current.

Now zoom in on the title block. Using the Place Field command place **Title**, **Revision**, **Date**, **Author**, **Filename**, **Sheet Number**, and **Number Of Sheets** fields into appropriate sections of the title block. Values are filled in for fields known to ACCEL EDA. Fields in braces (e.g., {Title}) have undefined values.

fields always contain current information

| Title {7 | Title}    |                      |             |

|----------|-----------|----------------------|-------------|

| Size     | Number    |                      | Rev         |

| А        |           | {Re                  | evision}    |

| Date     | {Date}    | Drawn by <b>{A</b> ( | uthor}      |

| Filename | Untitled2 | Sheet <b>1</b>       | of <b>1</b> |

status line magic

If you had trouble placing your fields accurately, the grid spacing is probably set too large. Let's switch to a finer grid. Instead of using the Options Grids command, type a new spacing (e.g., 25mil) directly into the grid box on the Status line. With a carriage return, the new grid value is made current. Select and drag your fields to center them between the lines.

Let's define the remaining values. Choose File Design Info. Fill in the text boxes, and click **OK**. Now redraw your screen using View Redraw and notice that the field values have been updated. Before opening your libraries, change back to a 100 mil grid by toggling the Grid Select button on the Status line. Use View All to display the entire sheet.

#### library setup

ACCEL Schematic is shipped with libraries containing over 20,000 components and you can add to this count by creating new ones. This evaluation comes with a small subset of components in a single library, DEMO.LIB. You can use these, create new components, or convert any P-CAD PDIF, Tango-Schematic (DOS), Schema, or Schemax library to ACCEL EDA format and use those components. For more information on using P-CAD files with ACCEL EDA, see Appendix A.

To open DEMO.LIB, choose Library Setup and click **Add.**Locate the file in the eval's Demo subdirectory, then click **OK**.

You now have access to any component in that library. ACCEL EDA allows multiple libraries to be opened at the same time, facilitating component organization.

### Creating a simple schematic

We'll start our schematic by creating a second sheet and then showing you a few ways to place parts and make connections.

more status line magic

In preparation of needing a second sheet, create one by choosing Options Sheets. Click the white box to the right of the current sheet name on the Status line to access the dialog without going through the menus. New sheets can be created any time during the design. Enter a new sheet name and click **Add**. Leave Sheet1 as the current sheet and close the dialog.

#### placing parts

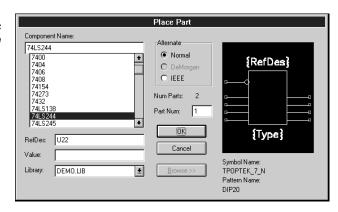

Now, we're ready to place a few parts on the schematic. Choose the Place Part icon, then click in the workspace. Choose the **Browse** button to graphically view the available parts and make sure you select the correct one.

browse library parts prior to placing them

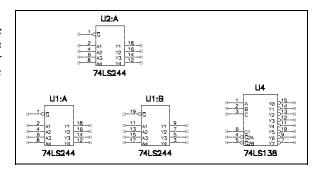

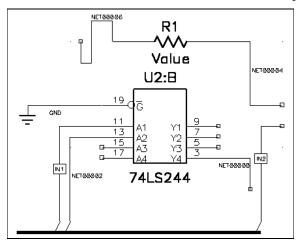

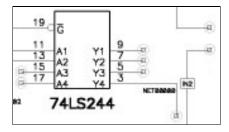

Pick 74LS244 from the **Component Name** list or start typing in the box and see how the list automatically scrolls to display parts having the given prefix. Notice **Num Parts** is set to 2, indicating two of these parts fit into one component package. Click **OK**.

Click in the workspace and drag the ghosted part below and to the left of the sheet's center, then release. Remember that your Zoom Window (Z), Zoom In (+), Zoom Out (-), Zoom Center (C), flip (F), and rotate (R) shortcut keys can be activated to control your display during placement.

The placed part was given a reference designator of U1:A. The Info box on the Status line indicates the next available RefDes is U1:B. Reference designators are assigned automatically and distinguish the multiple parts in a single package. Parts labeled U1:A and U1:B indicate they are two parts of the U1 component.

hotkeys let you change the RefDes on the fly By default the next 74LS244 part placed in the design is given the RefDes of U1:B. However, hotkeys are available to change it before placement. Press *P* and notice the part number on the Status line is sequentially incremented. *Shift+P* decrements the number. Similarly, *D* increments the RefDes and *Shift+D* decrements it. Press *Shift+D* until the RefDes returns to U1:B.

multi-part components are numbered automatically

Now, click in the workspace again, drag, and release to locate the second 74LS244 to the right of the first. Click the right mouse button or the *ESC* key to complete the placement.

drag and drop copy without extra keystrokes

Make a copy of one of the parts using drag and drop. Press S to invoke the select tool, then select U1:A. *Ctrl*+click left, drag to place a copied part above the first two parts, and release. Notice the copy is labeled U2:A, indicating it is the first part (A) of a new component (U2).

toggle between sheets using the status line

Let's place our next part on the second sheet. Toggle using the sheet Select or Scroll button on the Status line.

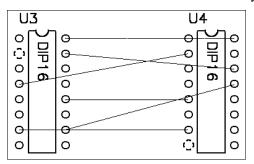

Use Place Part again, but this time choose 74154. Place it in the left half of the sheet and terminate by clicking the right mouse button. Note the reference designator is automatically set to U3.

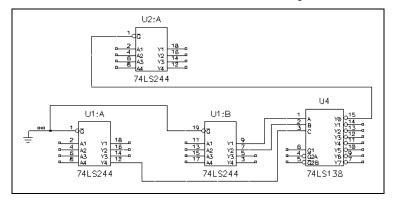

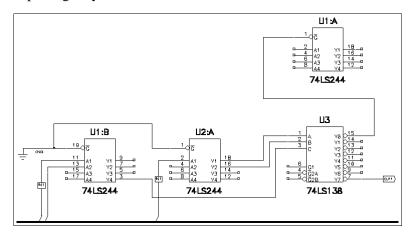

Toggle back to Sheet1 and place a 74LS138 to the right of U1:B. Your design on Sheet1 should now look something like this:

ACCEL Schematic automatically assigns reference designators for multi-part components

#### placing wires

Next we'll add a few connections. Choose the Place Wire tool from the Toolbar. Start at U1:B, pin 9 and connect U4, pin 1. In creating this connection, drag the wire diagonally and use the *O* and *F* keys to find the correct orthogonal mode and flip to the desired orientation. Notice on the Status line the wire is given a default name of NET00000. Finish your connection with a right mouse click. Add more wires to connect the input data lines for component U4: connect pin 7 of U1:B with pin 2 of U4, and pin 12 of U1:A with pin 3 of U4.

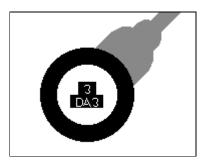

Now let's rename these nets to be clearly identified as data nets. Select the Utils Rename Net command and click in the workspace to bring up the Utils Rename Wire/Port dialog. Enter DATA1 as the net name and enable the **Increment Name** checkbox. Click **OK**. In turn, click a wire in each of the three nets you just created. This will re-name them DATA1, DATA2, and DATA3. A right mouse click (or *ESC*) terminates renaming.

ACCEL EDA allows you to start or end a wire without a pin. Choose the Place Wire icon again and place a wire starting at the left side of the sheet and ending at pin 1 of U1:A. A square should be displayed on the open end of the wire since we previously enabled the **Display Open Ends** option in Options Display. We could rename the net, but let's leave it set to the default.

sub-select the net name to move it effortlessly Make the net name visible by double clicking the wire to bring up the Properties dialog, and enabling the **Display** checkbox. Using sub-selection, move the name to a new location. To do this, press the *Shift* key at the same time you click the name. Release the *Shift* key and drag the name to the desired location.

placing GND automatically names the net Place a GND part on this open end. The box disappears, indicating the connection is complete. Notice the wire's net name was automatically changed to GND. This is accomplished because GND is defined as a Power part, and Power parts have an automatic net naming feature.

automatic junctions indicate net connections

Starting somewhere along the ground wire, use Place Wire to connect this net to U1:B, pin 19. Notice that a junction is automatically placed and the new wire is added to the ground net. Junction size can be changed from small to large with the Options Display command.

Now connect U4, pin 15 with U2:A, pin 1. Make the connection as shown, so we can later see how to move multiple items.

in just a few steps, your schematic is taking shape

#### placing buses

Next we'll add a data bus. Choose the Place Bus icon and add a horizontal bus below the placed parts. Next, place three separate wires to tie pins 2 and 4 of U1:A, and pin 11 of U1:B to the bus. Start or end your wire anywhere along the bus. There's no need to terminate with a right click; a bus entry is automatically placed. The entry style is the one previously selected using the Options Display command.

### placing ports

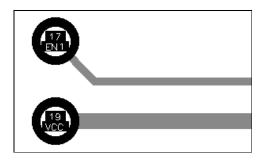

Two of the wires just placed belong to signal IN1. These wires are not physically connected, but carry the same signal. Ports are used to identify such unconnected subnets of a single net. They also allow you to explicitly identify subnets on one or more sheets, and their use prevents unintentional net merges. Choose the Place Port command and click in the workspace to view the dialog. Set the Net Name to IN1 and disable the Increment checkbox.

To place ports on the vertical wires, select options to create ports with two pins and a vertical orientation. Notice the preview box allows you to view the port's display before it is placed. After clicking **OK** to close the dialog, click and drag the port to the wire connecting pin 2 of U1:A with the bus. Place a second port on the wire connecting pin 11 of U1:B. Terminate placement with a right mouse click or *ESC* key.

### Working with your design

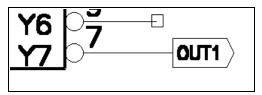

Cowabunga! We've nearly forgotten the part on our second sheet. Before we head over there, place a port directly onto pin 7 of U4, naming the net OUT1. Choose a port with one pin, horizontal orientation, and shaped to identify it as an off-sheet connector. Select the port and drag it away from the pin.

abutment wiring speeds design work Notice a wire was automatically added to fill the gap! This technique, called abutment routing or abutment wiring, can also be used to wire parts together without using the Place Wire command. You simply move the pins of one part on top of the pins of another, then separate the parts. Wires are added, connecting the once-overlapping pins.

moving to other sheets

We could toggle to the second sheet, but let's jump there instead. Choose Edit Parts and select U3 from the list. Click **Jump**. The sheet will change automatically and the cursor will be placed at the reference point of U3.

Place another port at pin 23 of U3, using the same OUT1 net name, and a port type that identifies it as an on-sheet connector. Recall that the *R* key can be used during placement to rotate a port. Select and drag the port to the left, away from the pin.

adding net attributes

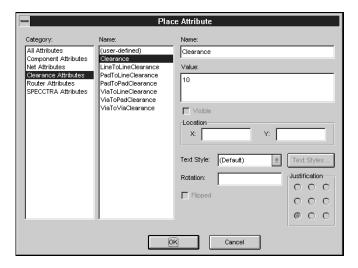

Now, let's add attributes to this net. Select the wire, click right, and choose **Edit Nets**. OUT1 is already selected. Click the **Edit Attrs** button. The box lists current attribute names and values. It will be blank. Press **Add** and examine the list of predefined attributes available for placement. (User-defined) attributes may

be added with any name and value you desire. These are useful when generating your own reports or interfacing to external programs. Choose the Clearance Attributes **Category**, pick the Clearance attribute **Name**, and enter a **Value** of 10.

net attributes assigned in the schematic can be used in the PCB

Press **OK** and you will see the newly added entry in the list. Net attributes are transferred in the ACCEL EDA netlist from the schematic to the PCB, where many are used for operations such as DRC, pin and gate swapping, and routing. Press **OK** and then **Close** to exit the dialogs.

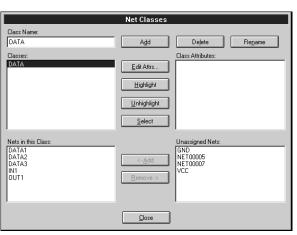

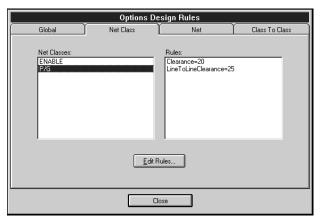

We can speed attribute assignment by grouping similar nets into a class, and assigning rules to the class. Using the Options Net Classes command, enter DATA as the **Class Name** and press **Add**.

apply design rules to a class of nets

Select the DATA\* nets in the **Unassigned Nets** box (press *Shift*+ select to access all of them at once) and press the <-**Add** button. Similarly, add the IN1 and OUT1 nets to the class. Click **Edit Attrs** to present the familiar Attributes dialog box. Assign a **Clearance** attribute of 8 to the class.

Holy cow... net OUT1 has been given two conflicting clearances! Which one would be used for DRC? Ten, and here's why:

a hierarchy simplifies design rule assignment

ACCEL EDA maintains a hierarchy to simplify design rule assignment. You add global rules, then need to define only the exceptions. Exceptions can be given for a group of nets, a single net, or between groups of nets. Precedence for assigned rules is given in the following order:

- class-to-class (highest precedence)

- net

- net class

- design level (lowest precedence)

Rules assigned at the higher precedence level are used whenever there is a conflict. In our design, the Clearance value of 10 applied directly to the net will be used because net rules have a higher precedence than net class rules.

clearance rules from the schematic are used for routing and DRC Clearance attributes assigned to any level of the hierarchy and carried to the PCB using the netlist are recognized for design rule checking (DRC), manual and interactive routing, and the SPECCTRA routing products.

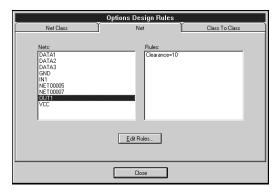

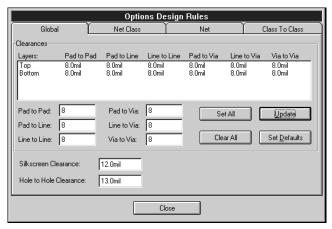

To view or edit hierarchical assignments, choose the Options Design Rules command. Look at our recent DATA net class and OUT1 net rule assignments. Use this command to view, add and edit design rules at any level.

design rules are accessed using one command

add a clearance to all two-node nets

One additional shortcut we'll introduce here is to select nets having a given number of nodes. This is helpful when applying rules to single- or double-node nets or the large nets as a group. With ACCEL EDA, it is easy to find these nets.

In the Edit Nets command dialog box, enter a **Min** value of 2 and **Max** number of 2 nodes. Click **Set Nets By Node Count** and notice all double node nets are identified in the **Net Names** box. Attributes can be added to all of these nets at the same time. Notice you can also use this command to highlight, select, and delete the identified nets.

probing nets across sheets

Nets and buses are easily probed across sheets. Use the Edit Parts command again, except this time choose U3 in the list and then click **Highlight Attached Nets**. The OUT1 wire is highlighted in the first highlight color. Toggle back to Sheet1 to easily locate OUT1 as the highlighted net on that sheet as well.

selecting a subnet or an entire net

Select any segment of the IN1 net; the one attaching U1:B to the bus. Click right and choose the **Select Contiguous** option. Notice only the physically connected wires are selected. Click right again, this time choosing the **Select Net** option. Notice now that the entire net is selected.

viewing the nets in a bus

If you ever need to recall what nets are attached to your bus, this information is readily available. Choose Edit Nets and select **Bus** in the **Type** box. Choose BUS00000 from the list of buses and its attached nets are then in the **Nodes** box.

making changes

Let's go back now and change our design to move U2:A closer to U4. Block select U2:A and the two wire segments closest to its pin 1. If you miss any of these, add to your selection with a *Ctrl*+click on the missing item. Move the items to the right so that U2:A is above U4. The long horizontal segment shortens automatically, maintaining connectivity.

moving multiple objects

If the component needs to be moved up to make space, the "horizontal" segment becomes non-orthogonal. Move your selection up a grid point. Adjust the display by selecting the diagonal segment and moving its left endpoint down a grid point to again create a 90-degree corner. Actually, you could have avoided the diagonal altogether if you had added the horizontal line to the selection (*Ctrl*+click) before moving the items up!

connectivity is maintained

Another facet of moving wires can be seen by selecting the vertical wire segment you had previously selected and moving it to the left and back to the right. Watch how connectivity is maintained. Remember that when moving items, you can always Undo (by pressing the *U* key or Undo Toolbar icon) to return them to their original locations.

renumbering designators

Before we verify our design and generate output, we should renumber our reference designators. To get a better idea of how renumbering works with different types of parts, place a few RES500 resistors on your sheet.

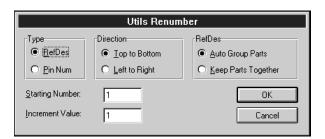

To renumber reference designators, choose the Select tool then use Utils Renumber.

renumber easily from top to bottom or left to right

Leave the dialog settings as they are and click **OK**. Your reference designators will be renumbered in top-to-bottom order within prefix types. In particular, your resistors are renumbered starting with R1, and the IC's are renumbered starting with U1. Notice also, renumbering of U3 and U4 was done across sheets.

adding values after placement

Select one or more resistors, then click right, and choose **Properties** from the pop-up menu. Enter a **Value**. Click **OK** and notice the Value field is updated for each part selected.

deleting parts

The resistors are really extraneous. Use the Options Block Selection command to select only the RES500 resistors for deletion. Click the **Clear All** button. Then toggle the **Part** checkbox until it is gray and the **Part** push button is enabled. Click the push button to bring up the Part Selection Mask dialog. Enter RES500 in the **Type** box and click **OK**. Choose the **Outside Block** selection mode and then **OK** to exit the dialog.

select all resistors on your sheet using block selection

Now click and drag in the workspace to create a block away from all resistors. All of your resistors should be selected. Delete them with the *delete* key, or by clicking the right mouse button and choosing **Delete** from the pop-up menu.

It is important to reset block selection using the Options Block Selection command. Choose the **Set All** push button and enable the **Inside Block** mode.

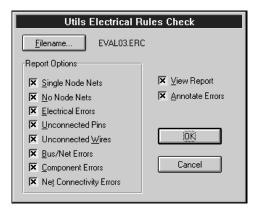

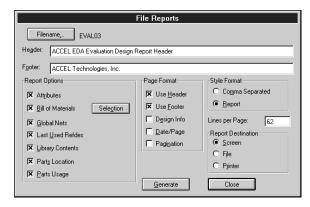

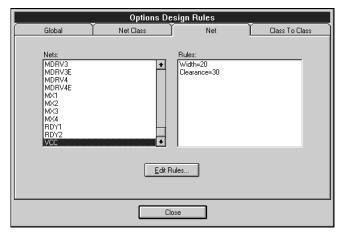

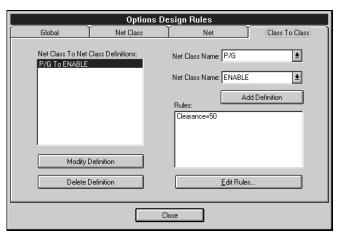

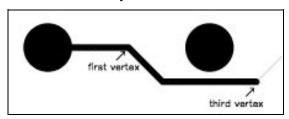

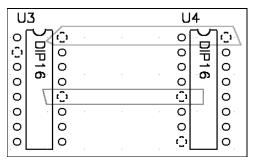

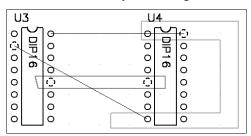

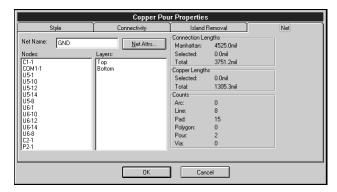

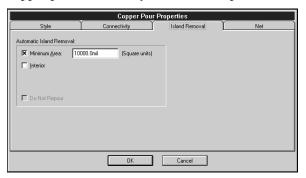

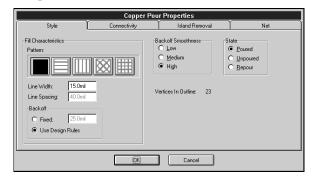

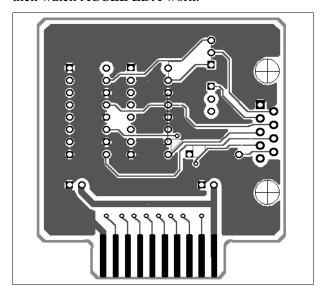

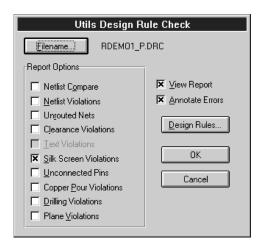

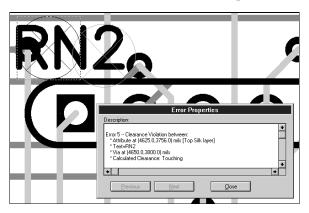

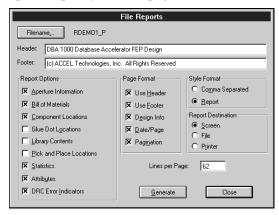

At this point, your design should look something like the following. If it does, congratulations! If not, you've been exploring on your own!